-1,File->New Project Wizard->弹出如下界面: -2,点击Next,弹出如下图所示对话框: -设置工程路径、工程名、顶层实体名,在这里注意工程名要和实体名保持一致,以免编译时出错。

-3,设置完成后点击Next,弹出Add Files对话框,如图: -如果没有文件需要添加,直接点击Next,如图: - 根据自己的需要设置好芯片系列、参数,然后选择正确的的芯片型号。

-4,点击Next,进入EDA Tool Settings对话框,如下图: -如果后续需要仿真或者需要使用第三方工具可以在这里设置

-5, 点击Next,进入Summary界面,如图: -此界面是关于新建立的工程详细信息报表,单击Finish完成。

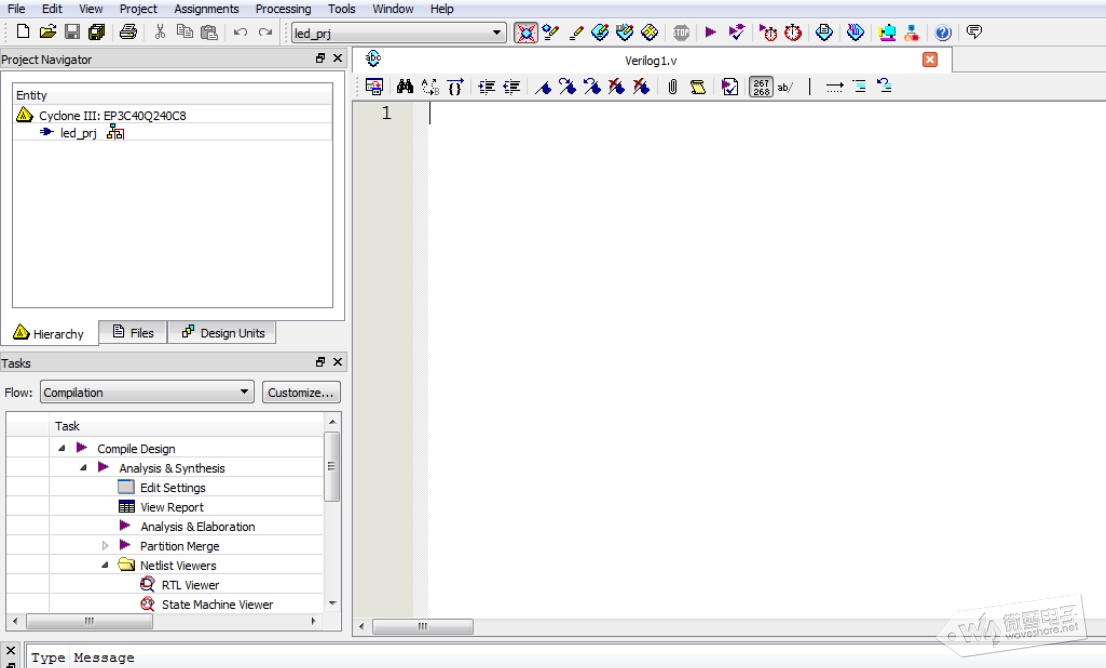

- File->New,选择 Design Files 下拉列表下的 Verilog HDL Files 选项,点击 OK,界面如下:

- 输入要编写的程序,注意:顶层实体名要和工程名一致。如下图:

- 点击保存按钮,保存到工程目录下。

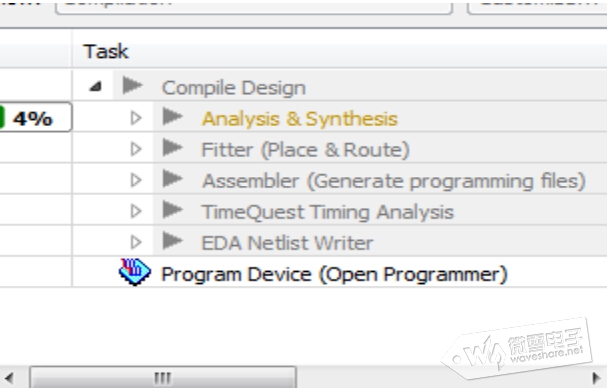

- Processing->start->Analysis&Synthesis(分析综合),如下图:

- 分配管脚及一些其它设置(这里只介绍常用设置,有兴趣的同学可以查阅 Altera 相关

文档)

Assignments->device,弹出如图所示对话框:

-

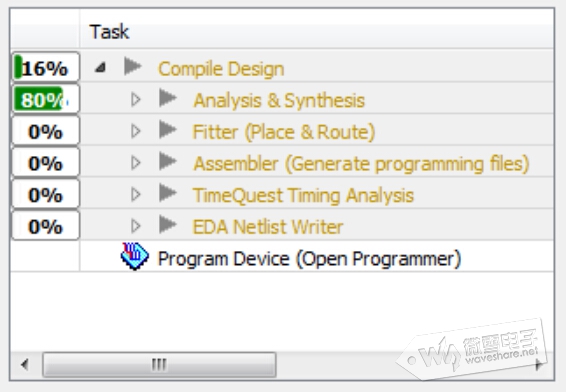

按照图示进行设置。注意:本开发板按 3.3V-LVTTL 电平进行设计 - Start->Compilation 进行编译,如下图:

- 完成后可进行下载或仿真。以下为本例程代码:

示例代码:10 | always@(posedge clk or negedge nrst) begin |

15 | else if (counter == 25000000) begin |

20 | counter <= counter + 25'd1; |

22 | always@(posedge clk2 or negedge nrst) begin |

26 | led_reg <= led_reg +4'd1; |

|