本节从总体上讨论ATtiny13 AVR 内核的结构。CPU 的主要任务是保证程序的正确执行。因此它必须能够访问存储器、执行运算、控制外设以及处理中断。

(点击图片放大)

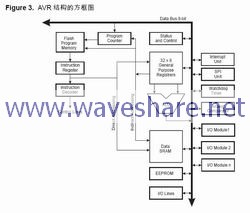

结构综述Figure 3. AVR 结构的方框图

为了获得最高的性能以及并行性, AVR 采用了Harvard 结构,具有独立的数据和程序总线。程序存储器里的指令通过一级流水线运行。CPU 在执行一条指令的同时读取下一条指令( 在本文称为预取)。这个概念实现了指令的单时钟周期运行。程序存储器是可以在线编程的FLASH。

快速访问寄存器文件包括32 个8 位通用工作寄存器,访问时间为一个时钟周期。从而实现了单时钟周期的ALU 操作。在典型的ALU 操作中,两个位于寄存器文件中的操作数同时被访问,然后执行运算,结果再被送回到寄存器文件。整个过程仅需一个时钟周期。

寄存器文件里有6 个寄存器可以用作3 个16 位的间接寻址寄存器指针以寻址数据空间,实现高效的地址运算。其中一个指针还可以作为程序存储器查询表的地址指针。这些附加的功能寄存器即为16 位的X、Y、Z 寄存器。

ALU支持寄存器之间以及寄存器和常数之间的算术和逻辑运算。ALU也可以执行单寄存器操作。运算完成之后状态寄存器的内容得到更新以反映操作结果。

程序流程通过有/ 无条件的跳转指令和调用指令来控制,从而直接寻址整个地址空间。大多数指令长度为16 位,亦即每个程序存储器地址都包含一条16 位或32 位的指令。

在中断和调用子程序时返回地址的程序计数器(PC) 保存于堆栈之中。堆栈位于通用数据SRAM,因此其深度仅受限于SRAM 的大小。在复位例程里用户首先要初始化堆栈指针SP。这个指针位于I/O 空间,可以进行读写访问。数据SRAM 可以通过5 种不同的寻址模式进行访问。

AVR 存储器空间为线性的平面结构。

AVR有一个灵活的中断模块。控制寄存器位于I/O空间。状态寄存器里有全局中断使能位。每个中断在中断向量表里都有独立的中断向量。各个中断的优先级与其在中断向量表的位置有关,中断向量地址越低,优先级越高。

I/O 存储器空间包含64 个可以直接寻址的地址,作为CPU 外设的控制寄存器以及其他I/O 功能。映射到数据空间即为寄存器文件之后的地址0x20 - 0x5F。