ATtiny13 系统时钟可通过设置时钟预分频寄存器 CLKPR 来分频。该特性可用来降低功 耗。该分频器对所有时钟源都有效,且可影响 CPU 时钟频率及所有同步外设。 clkI/O、 clkADC、clkCPU 及clkFLASH 分频因子见Table 9 。

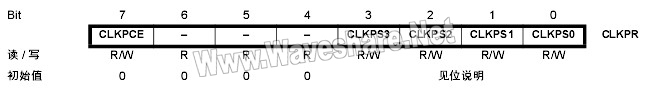

时钟预分频寄存器-CLKPR

· Bits 7 – CLKPCE: 时钟预分频器变化使能

CLKPCE 位必须置"1”使能 CLKPS位。只有当CLKPR寄存器的其他位同时写"0”时, CLK- PCE位改变。CLKPCE在写入四个周期后或当CLKPS位写入后由硬件清零。在暂停周期 中重新写 CLKPCE 位,既不扩展暂停周期,也不清除 CLKPCE 位。 · Bits 6..4 –Res: 保留

保留位,读操作返回值为零。 ·Bits 3..0 – CLKPS3..0: 时钟预分频器选择位 3 - 0

这几位定义所选时钟源与内部系统时钟所分频因子。这几位写入运行时间来改变时钟频 率以适应运行需要。当作为 MCU 主时钟输入分频器,使用分频因子时,所有同步外设速 度将会下降。分频因子见 Table 9。

为避免时钟频率的无意改变,对 CLKPS 位的写入必须按照如下步骤进行:

1. 将 CLKPCE位写 "1”,而 CLKPR 寄存器的其他位写 "0”。

2. 在四个时钟周期内,将期望值写入 CLKPS,并在 CLKPCE 位写 "0”。

在改变预分频器设置时必须禁止中断,以保证在写入过程中不会出现中断。

CKDIV8熔丝位决定CLKPS位的初始值。若CKDIV8未编程,CLKPS位复位为“0000”;若 CKDIV8 已编程,CLKPS 位复位为 “0011”,给出启动时分频因子为 8。若所选时钟源频率 大于当前工作状态下器件最大频率时,应利用该特性分频。注意,CLKPS 位写入值不受CKDIV8 熔丝位设置影响。若所选时钟源频率大于当前工作状态下器件最大频率,应用程 序必须保证选择一个足够大的分频因子。芯片出厂时 CKDIV8 熔丝位已编程。

转换时间

当预分频器转换时,系统时钟预分频器保证时钟系统中不会出现毛刺,且频率低于转换前后的频率。

脉动计数器使预分频器在未分频时钟频率下运行,这可能比 CPU 时钟频率快。因此即使预分频器可读,我们也无法确定其状态,所以我们也无法得到准确的转换时间。

CLKPS值的写入时间介于T1 + T2与T1 + 2*T2之间。在此间隔中,产生2个时钟边沿。其中 T1 为前一个时钟周期, T2 为新设置后相应的时钟周期。 |