状态寄存器包含了最近执行的算术指令的结果信息。这些信息可以用来改变程序流程以实现条件操作。如指令集所述,所有ALU 运算都将影响状态寄存器的内容。这样,在许多情况下就不需要专门的比较指令了,从而使系统运行更快速,代码效率更高。

在进入中断服务程序时状态寄存器不会自动保存,中断返回时也不会自动恢复。这些工作需要软件来处理。

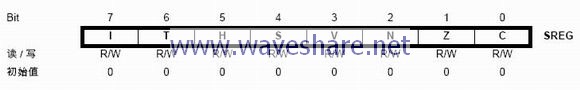

AVR 中断寄存器 SREG 定义如下:

·Bit 7 – I: 全局中断使能

I 置位时使能全局中断。单独的中断使能由其他独立的控制寄存器控制。如果I 清零,则不

论单独中断标志置位与否,都不会产生中断。任意一个中断发生后I 清零,而执行RETI

指令后I 恢复置位以使能中断。I 也可以通过SEI 和CLI 指令来置位和清零。

·Bit 6 – T: 位拷贝存储

位拷贝指令BLD 和BST 利用T 作为目的或源地址。BST 把寄存器的某一位拷贝到T,而

BLD 把T 拷贝到寄存器的某一位。

·Bit 5 – H: 半进位标志

半进位标志H 表示算术操作发生了半进位。此标志对于BCD 运算非常有用。详见指令集

的说明。

·Bit 4 – S: 符号位, S = N ⊕ V

S 为负数标志N 与2 的补码溢出标志V 的异或。详见指令集的说明。

·Bit 3 – V: 2 的补码溢出标志

支持2 的补码运算。详见指令集的说明。

·Bit 2 – N: 负数标志

表明算术或逻辑操作结果为负。详见指令集的说明。

·Bit 1 – Z: 零标志

表明算术或逻辑操作结果为零。详见指令集的说明。

·Bit 0 – C: 进位标志

表明算术或逻辑操作发生了进位。详见ATtiny13指令集的说明。

|