简介

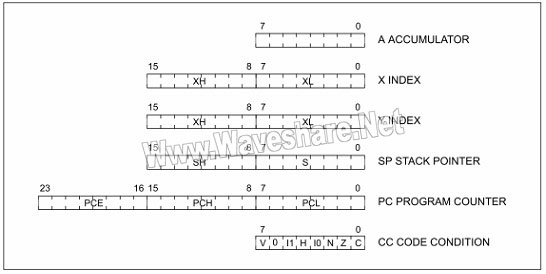

STM8S是基于8位框架结构的微控制器,其CPU内核有6个内部寄存器,通过这些寄存器可高效 地进行数据处理。STM8S的指令集支持80条基本 20种寻址模式,而且CPU的6个内部寄 存器都拥有可寻址的地址。如果想了解全部STM8S指令集,请参考STM8 微控制器家族编程手册 (PM0044)。 CPU寄存器

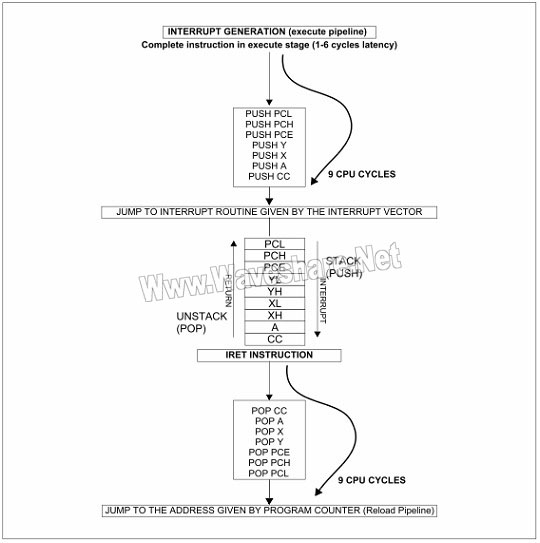

在图1所示的编程模型中可以看到6个CPU寄存器。在一个中断发生后,寄存器以图2所示顺序入栈,它们以相反的顺序出栈。如果需要的话,中断服务程序可使用POP和PUSH指令来对之进行操作。 CPU寄存器描述

- 累加器(A)

累加器是一个8位通用目的寄存器,用于保存算术运算、逻辑运算以及数据操作的操作数及结果。

- 索引寄存器(X和Y)

X和Y都是16位的寄存器,可实现高效率的寻址模式。它们也可用作数据操作的暂存器以及用于像乘除法这样的操作。在大多数情况下,交叉汇编器会在使用了Y寄存器的指令代码中生成PRECODE指令,用以和使用了X寄存器的指令相区别。

- 程序计数器(PC)

程序计数器是一个24位的寄存器,用于存储CPU下一条要执行指令的地址。其内容在每一次指令操作后被自动刷新。由于程序指针有24位,因此STM8的最大寻址范围可达16M字节。

(图1)

- 堆栈指针(SP)

堆栈指针是一个16位的寄存器,其内容为堆栈中下一个可自由分配的单元地址。根据不同的型号,堆栈指针的高位会有一个指定的预设值。

堆栈一般用于在中断调用或子程序调用时存储 CPU的上下文(程序计数器,关键寄存器,相关函数的参数及局部变量,等等)。用户也可以通过POP和PUSH指令直接对堆栈操作。

SP可以被C编译器的启动代码初始化,C语言应用程序会根据用户所使用的包含绝对地址信息的链接文件来进行初始化。如果用户使用了自己编写的链接文件和启动代码,请确认SP被恰当地初始化(具体地址信息请参考相应的数据手册)。在MCU复位后,或在执行了堆栈复位指令后(RSP),堆栈指针被设为其被允许的最大值。对于使用了汇编语言的应用程序,用户可使用ST提供的启动代码或编写自己的启动代码来对SP进行正确的初始化。

入栈操作使堆栈指针值减小,出栈操作使堆栈指针值增加。当堆栈指针值为其被允许的最小值时,继续入栈会使堆栈指针值回卷至其最大值,从而会导致先前存储的数据被覆盖,但此时没有中断或硬件标志位来指示该事件发生。应用程序需确保堆栈被正确的操作,没有溢出。

子程序调用会占用2或3字节空间。中断调用会占用9字节空间来存储内部寄存器(除SP之外)。请参考图2。

(图2)

*注:WFI/HLAT指令会预先保存CPU上下文。如果CPU处于WFI或HALT状态下有中断发生,则进入中断所需的延时会相应减少。

- 条件代码寄存器(CC)

条件代码寄存器是一个8位寄存器,用于指示刚刚被执行的指令结果及处理器的状态。寄存器的第7位(MSB)是保留位,这些位可以被用户的程序或代码单独地测试,测试的结果可用于指示程序或代码执行后的状态 。下面的段落将描述每一位的含义。- V:溢出

在上一次有符号数的算术操作中,如果结果的最高位有溢出发生,则当该位被置1。请参考INC,INCW,DEC,DECW,NEG,NEGW,ADD,ADDW,ADC,SUB,SUBW,SBC,CP,CPW等指令。

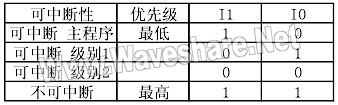

(表1)

- I1:中断屏蔽级别1

I1和I0共同用于指示当前状态下CPU的可中断性,请参考表1。通过执行RIM,SIM,HALT,WFI,IRET,TRAP和POP指令可对I1和I0置位或清零。I1和I0也会在CPU进入中断服务程序时被硬件自动设置为该中断对应的中断级别。 - H:半进位

在执行ADD或ADC操作的过程中,当ALU的第3位和第4位间发生进位时,H位会被置1,这对于

BCD码算术运算很有意义。 - I0:中断屏蔽级别0

请参考表1。 - N:负数

当上一次的算术、逻辑或数据操作的结果是负的情况下,N位被置1(例如结果的最高位是逻辑1)。 - Z:零

当上一次的算术、逻辑或数据操作的结果是零时,Z位被置1。 - C:进位

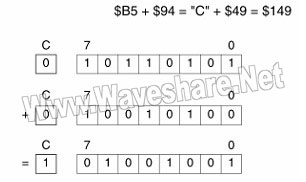

在上一次的算术操作中,如果结果的最高位发生进位或借位,则当该位被置1。当执行位测试,分支,移位,旋转和加载指令时,该位也会收到影响。请参考ADD,ADC,SUB, SBC等指令。

在除法操作中,C位用来指示在指令执行中是否有错误发生(商溢出或0作除数)。请参考DIV指令。

在位测试操作中,被测试的位被复制到C位;请参考BTJF,BTJT指令。在移位和旋转操作中,C位根据结果进行相应地更新;请参考RRC,RLC,SRL,SLL,SRA指令。

用户还可以通过SCF,RCF,CCF指令对C位进行置位,清除和取反。

例子:加法操作

|